# Neoverse Reference Design Platform Software

unknown

Apr 29, 2025

## ABOUT

| 1  | Reference Design              | 1  |

|----|-------------------------------|----|

| 2  | Software Stack                | 3  |

| 3  | Repo Tool & Manifests         | 7  |

| 4  | Troubleshooting               | 9  |

| 5  | Report Security Vulnerability | 13 |

| 6  | Getting Started               | 15 |

| 7  | Learning Paths                | 21 |

| 8  | RD-V3-R1-Cfg1 Platform        | 23 |

| 9  | RD-V3-R1 Platform             | 27 |

| 10 | RD-V3 Cfg2 Platform           | 31 |

| 11 | RD-V3 Cfg1 Platform           | 35 |

| 12 | RD-V3 Platform                | 39 |

| 13 | RD-V2 Platform                | 43 |

| 14 | RD-N2 Cfg3 Platform           | 45 |

| 15 | RD-N2 Cfg2 Platform           | 47 |

| 16 | RD-N2 Cfg1 Platform           | 49 |

| 17 | RD-N2 Platform                | 51 |

| 18 | RD-V1 MC Platform             | 53 |

| 19 | RD-V1 Platform                | 55 |

| 20 | RD-N1 Edge X2 Platform        | 57 |

| 21 | RD-N1 Edge Platform           | 59 |

| 22 | SGI-575 Platform              | 61 |

| 23 | AP Boot from BL31 (Reset to BL31 Flow)                    | 63  |

|----|-----------------------------------------------------------|-----|

| 24 | Boot Operating System(s)                                  | 65  |

| 25 | Compute Express Link                                      | 81  |

| 26 | MCP sideband channel                                      | 87  |

| 27 | Memory system resource Partitioning And Monitoring (MPAM) | 93  |

| 28 | Power Management                                          | 109 |

| 29 | Reliability, Availability, and Serviceability (RAS)       | 119 |

| 30 | SystemReady Compliance Program                            | 141 |

| 31 | TF-A Tests                                                | 147 |

| 32 | UEFI Self-Certification Test                              | 153 |

| 33 | Virtualization                                            | 161 |

| 34 | Virtio-P9                                                 | 185 |

| 35 | RD-INFRA-2025.02.04                                       | 189 |

| 36 | RD-INFRA-2024.12.20                                       | 193 |

| 37 | RD-INFRA-2024.09.30                                       | 199 |

| 38 | RD-INFRA-2024.07.15                                       | 205 |

| 39 | RD-INFRA-2024.04.17                                       | 211 |

| 40 | RD-INFRA-2024.01.16                                       | 219 |

| 41 | RD-INFRA-2023.12.22                                       | 225 |

| 42 | RD-INFRA-2023.09.29                                       | 229 |

| 43 | RD-INFRA-2023.09.28                                       | 233 |

| 44 | RD-INFRA-2023.06.30                                       | 237 |

| 45 | RD-INFRA-2023.06.28                                       | 241 |

| 46 | RD-INFRA-2023.03.31                                       | 245 |

| 47 | RD-INFRA-2023.03.29                                       | 249 |

### **REFERENCE DESIGN**

A Reference Design (RD) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP.

Specifically, Neoverse reference designs provide resources with best practices on how to integrate a Neoverse compute subsystem within a larger SoC. These compute subsystems are targeted at addressing requirements for applications in the cloud-to-edge infrastructure markets.

Neoverse products are categorized as follows:

- Neoverse V-Series: Maximum Performance

- Neoverse N-Series: Scale Out Performance

- Neoverse E-Series: Efficient Throughput

Refer to Arm Neoverse to learn more about the intended use cases for this products.

The Neoverse reference designs are also available as fixed virtual platform models and when used with a software stack, they provide a way to explore the features available in the reference design compute subsystem through software.

We provide a companion software stack for each of the Neoverse reference designs and the source code can be found in Arm's Gitlab repository, located at https://gitlab.arm.com/infra-solutions/reference-design

This documentation lists the available reference designs, the features each support and how to interact with them.

Note: A reference design is also referred to as platform.

Table below provides the user an overview of Neoverse reference designs, and their current status.

| Platform      | Status      |

|---------------|-------------|

| RD-V3-R1 Cfg1 | Active      |

| RD-V3-R1      | Active      |

| RD-V3 Cfg2    | Active      |

| RD-V3 Cfg1    | Active      |

| RD-V3         | Active      |

| RD-V2         | Maintenance |

| RD-N2 Cfg3    | Maintenance |

| RD-N2 Cfg2    | Maintenance |

| RD-N2 Cfg1    | Maintenance |

| RD-N2         | Maintenance |

| RD-V1         | Legacy      |

| RD-V1 MC      | Legacy      |

| RD-N1 Edge    | Legacy      |

| RD-N1 Edge X2 | Legacy      |

| SGI-575       | Legacy      |

Visit the *Getting Started* chapter to learn how to setup an host machine to download, compile and execute a platform feature (i.e.: boot an OS), on a fixed virtual platform.

For questions about the Neoverse Reference Design platform software stack, write to support@arm.com.

## SOFTWARE STACK

The Neoverse software stack integrates multiple software components to provide a reference implementation of a software solution that can be used demonstrate various capabilities of the respective platform.

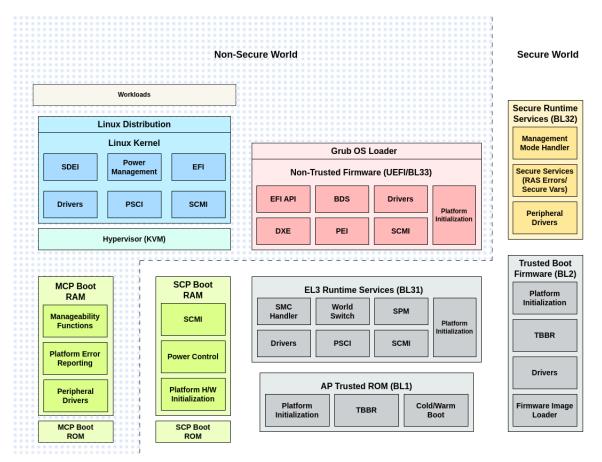

A typical software stack is illustrated in Fig. 2.1.

Fig. 2.1: High-level software illustration of a Neoverse Reference Design.

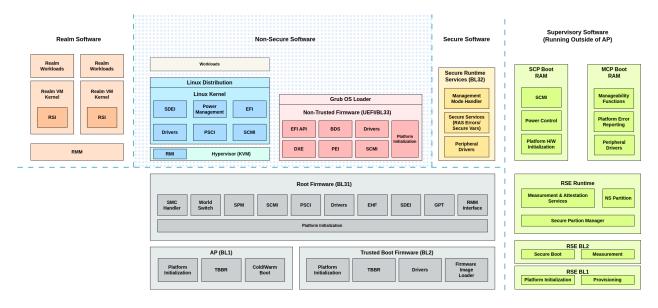

Some reference designs support the Realm Management Extension (RME), and their software stack is ilustrated in Fig. 2.2.

The following sections list the various software components that are included the Neoverse software stack.

Fig. 2.2: High-level software illustration of a Neoverse Reference Design with RME.

### 2.1 MSCP Firmware

Neoverse reference design platforms include a System Control Processor (SCP) sub-system and a Manageability Control Processor (MCP) sub-system. The SCP sub-system is tasked with the management of system clocks, power control, configuring the system interconnect, memory controllers, PCIe controllers and many other functionalities. The MCP sub-system is tasked with the management of communications with an external Baseboard Management Controller (BMC). The firmware executed by the SCP and MCP processors is sourced from the SCP-firmware open-source project.

## 2.2 Trusted Firmware

Trusted Firmware-A (TF-A) software component provides a reference open-source implementation of a secure monitor executing at EL3 exception level. It implements various Arm interface standards including the Power State Coordination Interface (PSCI), Trusted Board Boot Requirements (TBBR), SMC Calling Convention, System Control and Management Interface and others. The trusted firmware executes in various stages - Boot Loader stage 1 (BL1) AP Trusted ROM, Boot Loader stage 2 (BL2) Trusted Boot Firmware, Boot Loader stage 3-1 (BL3-1) EL3 Runtime Firmware, Boot Loader stage 3-2 (BL3-2) Secure-EL1 Payload (optional) and Boot Loader stage 3-3 (BL3-3) Non-trusted Firmware.

### 2.3 EDK2

EFI Development Kit 2 (edk2) is a firmware development environment for the UEFI and PI specifications. UEFI is a specification that defines an interface between the firmware and an Operating System (OS). UEFI defines the firmware interfaces and boot services that are required for booting a standards-based OS. UEFI also defines run-time services, for example, time, variable that an OS can invoke at runtime. The reference design platform stack integrates both the edk2 and edk2-platforms open-source projects to support an implementation of EFI API for the platform.

## 2.4 Linux Kernel

Linux kernel is used as the host operating system kernel for the reference design platforms. ACPI tables are used to describe the platform to the linux kernel. All the capabilities of the linux kernel are used to demonstrate the various functionalities of the platform software including power management, device assignment, RAS and many others.

## 2.5 Other software components

The platform software stack uses the following additional software components to provide an integrated software solution for the Neoverse reference design platforms.

- Trusted Firmware Test Framework

- Grub

- Busybox

- Buildroot

- ACPICA

- Mbed TLS

- ACS

- EFI Tools

- UEFI SCT

## **REPO TOOL & MANIFESTS**

repo tool is a wrapper around the git version control system to manage multiple git repositories, it simplifies several git operations, in particular the *sync* (download) of software sources to a local environment.

To achieve this, repo uses a manifest file, which is a collection of repositories with some attributes to specify for example the revision of a particular repository or the local path that repository will have once downloaded to our local environment.

### 3.1 Manifest File in Detail

A manifest file is written in Extensible Markup Language (XML), for a full list of supported elements and attributes please see repo manifest format.

Take the excerpt of an existing manifest file in Neoverse reference design gitlab repository to understand how manifests are defined.

Line #2, the element remote defines two attributes, fetch and name.

- **fetch** is the base url of a git repository.

- **name** is an alias for that repository.

Line #5, the element project also defines the attributes name, path and revision.

- **name** is the name of the project in the git repository.

- **path** is the local path where the project will be cloned to, relative to where the manifest is initialised.

- **revision** is the git revision to clone, this can be a *branch*, a *tag* or a *commit sha id*.

A remote can have multiple repositories, the link from a remote to a project is given by the alias set in line #2 and used in line #5 as remote="arm".

The revision attribute when set to *tag* or a *commit sha id* is what makes the software stack being reproducible because it will fetch the same software sources consistently. More details provided in the section *Pinned vs Non-Pinned*.

Translating the syntax of a manifest file to git, the underlying command of line #5 to run would be:

## 3.2 Manifest (Pinned vs Non-Pinned)

Now that the user knows how a manifest file is defined, let's stablish the concept of *Pinned* and *Non-Pinned* manifests.

When we release a software stack, we test the integration of all the components and validate that they work together to achieve the goal of providing users with a usable code base, thus we tag the manifest and the components to have a reference of this code base validity. This is the *Pinned* manifest and the file name convention is pinned-<platform>. xml.

But as software evolves, new features and/or security fixes will be made available in the participating components of the software stack, therefore we provide a manifest where the revision of the components is set to a branch that is updated more frequently with their upstream counterparts. This is the *Non-Pinned* manifest, and the file name simply is the platform name, i.e.: <platform>.xml.

### TROUBLESHOOTING

The documentation for Neoverse reference design platform software typically suffices in most cases. But there could be certain host development machine dependencies that could cause failures either during build or execution stages. This page provides solutions for known issues that could affect the use of the platform software stack.

### 4.1 Error while using repo command

The repo init or repo sync command fails with the below listed error message.

The typical reason for this failure could be that the default version of python on the development machine is not python3.6. To resolve this issue, install the latest version of python, if not already installed on the development machine and invoke the repo command from */usr/bin/* with *python3* as listed below.

On systems with python version less than 3.6, there could be further failures as listed below.

SyntaxError: invalid syntax

If *python3* version cannot be updated using the package manager, use the following commands to build and install *python3.7.2* from the source.

```

sudo apt update

sudo apt install build-essential zlib1g-dev libncurses5-dev libgdbm-dev libnss3-dev_

→libssl-dev libreadline-dev libffi-dev wget libsqlite3-dev python-openss1 bzip2

```

(continues on next page)

(continued from previous page)

```

cd /tmp

wget https://www.python.org/ftp/python/3.7.2/Python-3.7.2.tar.xz

tar -xf Python-3.7.2.tar.xz

cd Python-3.7.2

./configure

make -j

sudo make altinstall

```

This will install *python3.7* in */usr/local/bin/* path and the *repo* command can be invoked using this version.

```

/usr/local/bin/python3.7 /usr/bin/repo init -u https://git.gitlab.arm.com/infra-

→solutions/reference-design/infra-refdesign-manifests.git -m pinned-rdv1.xml -b refs/

→tags/RD-INFRA-2021.02.24

/usr/local/bin/python3.7 /usr/bin/repo sync -c -j $(nproc) --fetch-submodules --force-

→sync --no-clone-bundle

```

### 4.2 Builds do not progress to completion

During the build of the platform software stack, components such as grub download additional code from remote repositories using the git port (or the git protocol). Development machines on which git port is blocked, the build does not progress to completion, waiting for the additional code to be downloaded. This typically is observed when setting up a new platform software workspace.

As a workaround, use https instead of git protocol for cloning required git submodules of the various components in the software stack. A patch, as an example of this change in the grub component, is listed below.

```

diff --git a/bootstrap b/bootstrap

index 5b08e7e2d..031784582 100755

--- a/bootstrap

+++ b/bootstrap

@@ -47,7 +47,7 @@ PERL="${PERL-perl}"

me=$0

-default_gnulib_url=git://git.sv.gnu.org/gnulib

+default_gnulib_url=https://git.savannah.gnu.org/git/gnulib.git

usage() {

cat <<EOF</pre>

```

## 4.3 FVP closes abruptly

Tests such as distro installation take few hours to complete on Neoverse Reference Design platform FVPs. If the model quits abruptly during its execution without any particular error message displayed in the model launch window, the host machine's memory requirements has to be rechecked. This issue is typically seen if the host machine has a configuration below that of on the one listed at *recommended configuration*.

Repo sync fails when downloading linux repo

If the download of the linux repo fails during the execution of the *repo sync* command, rerun the repo init command with the --depth=1 parameter appended to the repo init command. The parameter --depth=1 reduces the commit history that is downloaded and can address this failure in downloading linux repo.

## 4.4 Error: "/usr/bin/env: 'python': No such file or directory"

repo init could fail if it can't find a compatible reference to python. Please make sure you have the required version of python as mentioned in *install repo* prerequisites section.

If the error still persists, check if */usr/bin* has a binary named python. If you find the binary name to be *python3* (or any *python3.x* for that matter) and */usr/bin/python* is not found, then create a softlink to work around this issue as shown below:

sudo ln -s /usr/bin/python3 /usr/bin/python

### **REPORT SECURITY VULNERABILITY**

Arm Neoverse reference design software solutions are example software projects containing downstream versions of open source components. Although the components in these solutions track their upstream versions, users of these solutions are responsible for ensuring that, if necessary, these components are updated before use to ensure they contain any new functional or security fixes that may be required.

If you think you have found a security vulnerability in a specific open source project which is part of the software stack, it is recommended to follow the vulnerability reporting guidelines specified by the respective project.

If you think you have found a security vulnerability as part of the Neoverse Reference Design platform software stack and does not fall into any specific open source project, then please report it specifying the project name as "Neoverse Reference Design Platform Software". More details on how to report can be found at Arm Developer website.

### **GETTING STARTED**

### 6.1 Prerequisites

#### **Important:**

- Neoverse software stack builds are only supported in linux operating systems.

- The operating system used to validate these instructions is Ubuntu 22.04 (althought any modern linux distribution should work).

- The following sections and chapters assume the commands are executed in a bash shell environment.

Host machine recommended hardware configuration:

- AArch64 or x86-64 architecture host.

- 64GB of free disk space.

- 48GB of RAM (32GB minimum).

The host machine needs the following packages installed.

```

sudo apt update

sudo apt install curl git

```

Configure git as follows.

```

git config --global user.name "<your-name>"

git config --global user.email "<your-email@example.com>"

```

Install repo tool via 'manual method'. Refer to repo install official documentation as this might change. Instructions provided here for convinience.

```

export REPO=$(mktemp /tmp/repo.XXXXXXXX)

curl -o ${REPO} https://storage.googleapis.com/git-repo-downloads/repo

gpg --recv-keys 8BB9AD793E8E6153AF0F9A4416530D5E920F5C65

curl -s https://storage.googleapis.com/git-repo-downloads/repo.asc | gpg --verify - $

$

$\leftarrow \{REPO\} && install -m 755 $\{REPO\} \circle bin/repo

```

**Warning:** The repo tool requires at least Python 3.6 to be installed on the development machine. On machines where python3 is not the default, the repo init command will fail to complete. Refer the *troubleshooting guide*.

### 6.2 Download Sources

In the previous section the host machine is configured with the minimum set of tools to allow the user to prepare and *sync* a workspace. This workspace will then configure a build environment, but more on that in the next section.

This workspace is a folder in the user host machine that contains all of the software sources, as well as, build products once a build is successful and complete.

This guide refers to this folder as <workspace> but the user is encouraged to provide a meaningful name.

Create a folder, and change directory to it.

```

mkdir <workspace>

cd <workspace>

```

Initialise and sync (download) the sources. The command below is the generic form and requires <manifest-file-name> and <RELEASE\_TAG> to be replaced by valid arguments.

- Manifest file names can be found here.

- Release tags are located in *Release Tags* section of each supported platform user guide or from the release notes.

```

repo init -u https://git.gitlab.arm.com/infra-solutions/reference-design/infra-refdesign-

→manifests.git -m <manifest-file-name> -b refs/tags/<RELEASE_TAG> --depth=1

repo sync -c -j $(nproc) --fetch-submodules --force-sync --no-clone-bundle

```

**Hint:** To reduce the size of the commit history that is downloaded (thus reducing the time taken to download the platform software stack), the repo init command above is append with --depth=1. If the user requires more commit history, the argument can be removed before executing the command.

### 6.3 Build Environment

There are two methods to build the reference stack - host based and container based. The host based build is the traditional one in which a script is executed to install all the build dependencies on the host machine. The container based build is an another method in which a container image is built from a container configuration file and has all the build dependencies satisfied and isolated from the host machine.

Both of the methods assume the user has completed the section *Download Sources*.

### 6.3.1 Host Based

For setting up the build environment in this method, execute the following command before building the software stack. The execution of this script installs all the build dependencies.

**Note:** This command installs additional packages on the host machine and so the user is expected to have sufficient privileges on the host machine.

./build-scripts/rdinfra/install\_prerequisites.sh

### 6.3.2 Container Based

Note: The supported container engine is docker.

Warning: Rootless support changes are distruptive and not compatible with old images. Please build image again.

The container image is designed to allow a user to have the sources directory (<workspace>) in the host machine and offload the build stage to the container, thus a user is created inside the container with the same username, user-id and user-group as the user on the linux host machine.

This approach allows a user to have the binaries built by the container and use IDE's like ARM DS to execute debug sessions, as paths and permissions are the same wether inside or outside the container.

#### **Install Container Engine**

Please refer to docker install instructions as there are several methods available, ensuring you install the following *docker-engine* and optionally the *buildx-plugin*.

After installation is complete, refer to the post-installation steps on how to manage docker as non-root user.

#### **Build Container Image**

**Warning:** Do **not** execute the wrapper script with root permissions. As doing so, interferes with permissions and will lead to errors when building and executing software.

The wrapper script *container.sh* sets the container file and image name by default and this can be changed with options *-f* and *-i* respectively or by editing the file itself. To see all options available, execute the script with the help flag.

cd <workspace>/container-scripts

./container.sh -h

To build the container image, execute:

./container.sh build

#### **Run Container Image**

Mount the <workspace> directory in the container by using the option -v followed by the absolute path to <workspace>. The mount point inside the container is the exact same path as the host system. To run the container image, execute the following:

./container.sh -v /absolute/path/to/rd-infra run

The container shall be running and the shell prompt display:

\$USER:\$HOSTNAME:<path\_to\_rd-infra>\$

As this is designed to have the same user and hostname as the host, it is not straightforward to see the container is executing, but a way to verify it is to check **.dockerenv** file, thus execute:

\$ls -la /.dockerenv

#### **Rootless Docker Support**

Rootless docker support has been added to **container.sh** wrapper script. It will check the current docker context and if rootless is activated it will run containers as rootless containers.

This completes the procedure to setup the container-based build environment.

### 6.4 Enable Network for FVP's (optional)

If networking is required, the platform FVP's support a virtual ethernet interface that can be configured via TAP mode interface. This mode allows the FVP to be directly connected to the network via a bridge. All ports are forwarded to the FVP networking interface as if it was connected to the network.

#### 6.4.1 Host Dependencies

**Note:** This command installs additional packages on the host machine and so the user is expected to have sufficient privileges on the host machine.

```

sudo apt update

sudo apt install qemu-kvm libvirt-daemon-system iproute2

```

#### 6.4.2 Configure TAP Interface

Ensure that the libvirtd service is running

sudo systemctl start libvirtd

Create a network bridge and change state to up. This step is only required once, so the user can skip if a bridge exists.

This example uses virbr0 for the bridge name.

sudo ip link add name virbr0 type bridge

sudo ip link set dev virbr0 up

Finally, the TAP interface is created, configured and attached to virbr0.

sudo ip tuntap add dev tap0 mode tap user \$(whoami)

sudo ip link set tap0 promisc on

sudo ip addr add 0.0.0.0 dev tap0

sudo ip link set tap0 up

sudo ip link set tap0 master virbr0

This completes the environment setup to have a working workspace so the user can proceed to build, and experiment with Neoverse reference designs features.

Refer the *Troubleshooting Section* for solutions to known issues that might arise during use of the platform software stack.

### **LEARNING PATHS**

Arm Learning Paths, available on the Developer Hub, are community-created how-to articles about software development for the Arm architecture. They offer detailed tutorials designed to help developers create quality Arm software faster. A Learning Path is a concise tutorial with detailed steps on how to complete a specific task.

The Learning Paths are segmented into categories, each covering different kinds of computer hardware. These categories include Smartphones and Mobile, Laptops and Desktops, Servers and Cloud Computing, Embedded Systems, and Microcontrollers. Neoverse Reference Designs are a part of servers and cloud computing.

The sections below list the available learning paths that are applicable to Neoverse Reference Designs.

### 7.1 Get started with the Neoverse Reference Design software stack

Follow the link below for this tutorial:

https://learn.arm.com/learning-paths/servers-and-cloud-computing/refinfra-quick-start/

### 7.2 Debug Neoverse N2 Reference Design with Arm Development Studio

Follow the link below for this tutorial:

https://learn.arm.com/learning-paths/servers-and-cloud-computing/refinfra-debug/

### EIGHT

### **RD-V3-R1-CFG1 PLATFORM**

### 8.1 Overview

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP.

RD-V3-R1-Cfg1 is a quad-chip platform in which four identical chips are connected through high speed CCG link. The CCG link is enabled through CMN-Cyprus Coherent Multichip Link (CML) feature. RD-V3-R1-Cfg1 platform (a variant of the *RD-V3-R1* platform) also supports the Realm Management Extension (RME). The RD-V3-R1-Cfg1 platform in particular has the following hardware configuration on each chip.

- Up to 8xMP1 Neoverse Poseidon-V3 cores with Direct Connect and 2MB of dedicated, private L2 cache for each core.

- 2 Shared LCP Groups, 4 AP cores per Shared LCP Group.

- CMN S3 Revision 2 interconnect with 3x4 mesh network.

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M55 processor for Runtime Security Engine (RSE) to support Hardware Enforced Security (HES)

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

- Arm Cortex-M55 processor for Local Control Processor (LCP) for local power management of each Application Processor (AP)

The Fixed Virtual Platform of RD-V3-R1-Cfg1 config supports quad chip with 8xMP1 Neoverse Poseidon-V3 CPUs per chip.

The components integrated into this stack are described in *Software Stack* section.

### 8.2 Platform Specific Details

The following documents provide specific details applicable for RD-V3-R1-Cfg1 Platform:

- Boot Flow

- CMN Cyprus Driver Module

- CMN Cyprus Multichip Configuration

- Image Loading via MCUboot

- Local Control Processor

- Multichip Memory Map

- NI-Tower System Control

- Realm Management Extension

- Runtime Security Engine

- SCP Address Translation Unit Configuration

- SCP RSE Communication

### 8.3 Supported Features

RD-V3-R1-Cfg1 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Linux Distribution Boot

- Low power idle

- Collaborative processor performance control

Follow the links above for detailed information about the build and execute steps for each of the supported features.

## 8.4 Obtaining FVP

The latest version of the RD-V3-R1-Cfg1 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse V3 r1 Reference Design FVP" link to obtain the list of available Neoverse RD-V3-R1-Cfg1 Reference Design FVPs.

- Select a FVP build under the section "Download RD-V3-R1-Cfg1" based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-V3-R1-Cfg1 FVP executable is included in the downloaded installer and named as "FVP\_RD\_V3\_R1". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

## 8.5 Release Tags

Table below lists the release tags for the RD-V3-R1-Cfg1 platform software stack and the corresponding RD-V3-R1-Cfg1 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-V3-R1-Cfg1 FVP Version |

|---------------------|---------------------------|

| RD-INFRA-2025.02.04 | 11.27.51                  |

| RD-INFRA-2024.12.20 | 11.27.51                  |

| RD-INFRA-2024.09.30 | 11.27.25                  |

### NINE

## **RD-V3-R1 PLATFORM**

### 9.1 Overview

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP.

RD-V3-R1 is a dual-chip platform in which two identical chips are connected through high speed CCG link. The CCG link is enabled through CMN S3 Coherent Multichip Link (CML) feature. RD-V3-R1 platform also supports the Realm Management Extension (RME). The RD-V3-R1 platform in particular has the following hardware configuration on each chip.

- Up to 70xMP1 Neoverse Poseidon-V3 cores with Direct Connect and 2MB of dedicated, private L2 cache for each core.

- 7 Shared LCP Groups, 10 AP cores per Shared LCP Group.

- CMN S3 Revision 2 (CMN S3 R2) interconnect with 9x8 mesh network.

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M55 processor for Runtime Security Engine (RSE) to support Hardware Enforced Security (HES)

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

- Arm Cortex-M55 processor for Local Control Processor (LCP) for local power management of each Application Processor (AP)

The Fixed Virtual Platform of RD-V3-R1 config supports dual chip with 14xMP1 Neoverse Poseidon-V3 CPUs per chip (2 AP cores per LCP Group)

The components integrated into this stack are described in *Software Stack* section.

### 9.2 Platform Specific Details

The following documents provide specific details applicable for RD-V3-R1 Platform:

- Boot Flow

- CMN Cyprus Driver Module

- CMN Cyprus Multichip Configuration

- Image Loading via MCUboot

- Local Control Processor

- Multichip Memory Map

- NI-Tower System Control

- Realm Management Extension

- Runtime Security Engine

- SCP Address Translation Unit Configuration

- SCP RSE Communication

### 9.3 Supported Features

RD-V3-R1 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Linux Distribution Boot

- Low power idle

- Collaborative processor performance control

Follow the links above for detailed information about the build and execute steps for each of the supported features.

## 9.4 Obtaining FVP

The latest version of the RD-V3-R1 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse V3 r1 Reference Design FVP" link to obtain the list of available Neoverse RD-V3-R1 Reference Design FVPs.

- Select a FVP build under the section "Download RD-V3-R1" based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-V3-R1 FVP executable is included in the downloaded installer and named as "FVP\_RD\_V3\_R1". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

## 9.5 Release Tags

Table below lists the release tags for the RD-V3-R1 platform software stack and the corresponding RD-V3-R1 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-V3-R1 FVP Version |

|---------------------|----------------------|

| RD-INFRA-2025.02.04 | 11.27.51             |

| RD-INFRA-2024.12.20 | 11.27.51             |

| RD-INFRA-2024.09.30 | 11.27.25             |

### **RD-V3 CFG2 PLATFORM**

### **10.1 Overview**

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-V3-Cfg2 platform is a quad chip variant of the RD-V3 platform.

RD-V3-Cfg2 is a quad-chip platform in which four identical chips are connected through high speed CCG link. The CCG link is enabled through CMN-Cyprus Coherent Multichip Link (CML) feature. The RD-V3-Cfg2 platform in particular has the following hardware configuration on each chip.

- 4x32XMP1 Neoverse Poseidon-V cores with Direct Connect and 2MB of dedicated, private L2 cache for each core.

- CMN-Cyprus interconnect with 7x6 mesh network.

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M55 processor for Runtime Security Engine (RSE) to support Hardware Enforced Security (HES)

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

- Arm Cortex-M55 processor for Local Control Processor (LCP) for local power management of each Application

Processor (AP)

The Fixed Virtual Platform of RD-V3-Cfg2 config supports quad chip with 4xMP1 Neoverse Poseidon-V CPUs per chip.

The components integrated into this stack are described in Software Stack section.

### **10.2 Platform Specific Details**

The following documents provide specific details applicable for RD-V3-Cfg2 Platform:

- Boot Flow

- CMN Cyprus Driver Module

- CMN Cyprus Multichip Configuration

- Image Loading via MCUboot

- Local Control Processor

- Multichip Memory Map

- NI-Tower System Control

- Realm Management Extension

- Runtime Security Engine

- SCP Address Translation Unit Configuration

- SCP RSE Communication

## **10.3 Supported Features**

RD-V3-Cfg2 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Low power idle

- Collaborative processor performance control

- AP Reset to BL31

Follow the links above for detailed information about the build and execute steps for each of the supported features.

## 10.4 Obtaining FVP

The latest version of the RD-V3-Cfg2 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse V3 Reference Design FVP" link to obtain the list of available Neoverse RD-V3 Reference Design FVPs.

- Select a FVP build under the section "Download RD-V3" based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-V3-Cfg2 FVP executable is included in the downloaded installer and named as "FVP\_RD\_V3\_Cfg2". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

## 10.5 Release Tags

Table below lists the release tags for the RD-V3-Cfg2 platform software stack and the corresponding RD-V3-Cfg2 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-V3-Cfg2 FVP Version |

|---------------------|------------------------|

| RD-INFRA-2025.02.04 | 11.27.51               |

| RD-INFRA-2024.12.20 | 11.27.51               |

| RD-INFRA-2024.09.30 | 11.27.25               |

| RD-INFRA-2024.07.15 | 11.26.15               |

| RD-INFRA-2024.04.17 | 11.24.16               |

| RD-INFRA-2024.01.16 | 11.24.16               |

| RD-INFRA-2023.09.28 | 11.23.11               |

| RD-INFRA-2023.06.28 | 11.22.16               |

#### ELEVEN

# **RD-V3 CFG1 PLATFORM**

## **11.1 Overview**

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-V3-Cfg1 platform (a variant of the *RD-V3* platform) also supports the Realm Management Extension (RME) and is based on the following hardware configuration.

- 8xMP1 Neoverse Poseidon-V cores with Direct Connect and 2MB of dedicated, private L2 cache for each core.

- CMN-Cyprus interconnect with 3x3 mesh network.

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M55 processor for Runtime Security Engine (RSE) to support Hardware Enforced Security (HES)

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

- Arm Cortex-M55 processor for Local Control Processor (LCP) for local power management of each Application Processor (AP)

The components integrated into this stack are described in *Software Stack* section.

# **11.2 Platform Specific Details**

The following documents provide specific details applicable for RD-V3-Cfg1 Platform:

- AP RSE Attestation Service

- Boot Flow

- CMN Cyprus Driver Module

- Image Loading via MCUboot

- Local Control Processor

- NI-Tower Network-on-Chip Interconnect

- NI-Tower System Control

- Realm Management Extension

- Runtime Security Engine

- SCP Address Translation Unit Configuration

- SCP RSE Communication

# **11.3 Supported Features**

RD-V3-Cfg1 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Linux Distribution Boot

- UEFI Secure Boot

- Reliability, Availability, and Serviceability

- Poseidon CPU/RAM Error Injection Tests

- CMN Cyprus Kernel First Handling

- SCP Error Injection Utility

- MPAM-resctrl

- Low power idle

- Collaborative processor performance control

- AP Reset to BL31

# 11.4 Obtaining FVP

The latest version of the RD-V3-Cfg1 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse V3 Reference Design FVP" link to obtain the list of available Neoverse RD-V3-Cfg1 Reference Design FVPs.

- Select a FVP build under the section "Download RD-V3-Cfg1" based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-V3-Cfg1 FVP executable is included in the downloaded installer and named as "FVP\_RD\_V3\_Cfg1". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 11.5 Release Tags

Table below lists the release tags for the RD-V3-Cfg1 platform software stack and the corresponding RD-V3-Cfg1 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-V3-Cfg1 FVP Version |

|---------------------|------------------------|

| RD-INFRA-2025.02.04 | 11.27.51               |

| RD-INFRA-2024.12.20 | 11.27.51               |

| RD-INFRA-2024.09.30 | 11.27.25               |

| RD-INFRA-2024.07.15 | 11.26.15               |

| RD-INFRA-2024.04.17 | 11.24.16               |

| RD-INFRA-2024.01.16 | 11.24.16               |

| RD-INFRA-2023.09.28 | 11.23.11               |

| RD-INFRA-2023.06.28 | 11.22.16               |

| RD-INFRA-2023.03.29 | 11.21.18               |

#### TWELVE

# **RD-V3 PLATFORM**

## 12.1 Overview

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-V3 is the first RD platform with Realm Management Extension (RME) support and is based on the following hardware configuration.

- 32xMP1 Neoverse Poseidon-V cores with Direct Connect and 2MB of dedicated, private L2 cache for each core.

- CMN-Cyprus interconnect with 7x6 mesh network.

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M55 processor for Runtime Security Engine (RSE) to support Hardware Enforced Security (HES)

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

- Arm Cortex-M55 processor for Local Control Processor (LCP) for local power management of each Application

Processor (AP)

The Fixed Virtual Platform of RD-V3 config supports 16xMP1 Neoverse Poseidon-V CPUs.

The components integrated into this stack are described in Software Stack section.

# **12.2 Platform Specific Details**

The following documents provide specific details applicable for RD-V3 Platform:

- AP RSE Attestation Service

- Boot Flow

- Chain of Trust (CoT) for CCA

- CMN Cyprus Driver Module

- Image Loading via MCUboot

- Local Control Processor

- NI-Tower Network-on-Chip Interconnect

- NI-Tower System Control

- Realm Management Extension

- Runtime Security Engine

- SCP Address Translation Unit Configuration

• SCP - RSE Communication

# **12.3 Supported Features**

RD-V3 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Linux Distribution Boot

- Arm SystemReady Compliance

- UEFI Secure Boot

- Low power idle

- Collaborative processor performance control

- Reboot-Shutdown test

- RD-V3 SMCF test

- AP Reset to BL31

- Virtualization

- IO virtualization

- Virtual Interrupts And VGIC

- KVM Unit Test

- Booting Distro as a VM

# 12.4 Obtaining FVP

The latest version of the RD-V3 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse V3 Reference Design FVP" link to obtain the list of available Neoverse RD-V3 Reference Design FVPs.

- Select a FVP build under the section "Download RD-V3" based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-V3 FVP executable is included in the downloaded installer and named as "FVP\_RD\_V3". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 12.5 Release Tags

Table below lists the release tags for the RD-V3 platform software stack and the corresponding RD-V3 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-V3 FVP Version |

|---------------------|-------------------|

| RD-INFRA-2025.02.04 | 11.27.51          |

| RD-INFRA-2024.12.20 | 11.27.51          |

| RD-INFRA-2024.09.30 | 11.27.25          |

| RD-INFRA-2024.07.15 | 11.26.15          |

| RD-INFRA-2024.04.17 | 11.24.16          |

| RD-INFRA-2024.01.16 | 11.24.16          |

| RD-INFRA-2023.09.28 | 11.23.11          |

| RD-INFRA-2023.06.28 | 11.22.16          |

| RD-INFRA-2023.03.29 | 11.21.18          |

### THIRTEEN

## **RD-V2 PLATFORM**

### 13.1 Overview

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-V2 in particular is based on the following hardware configuration.

- 32xMP1 Neoverse V2 CPUs

- CMN-700 interconnect (mesh size 6x6)

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

The Fixed Virtual Platform of RD-V2 config supports 16xMP1 Neoverse V2 CPUs.

The components integrated into this stack are described in Software Stack section.

# **13.2 Supported Features**

RD-V2 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Linux Distribution Boot

- Arm SystemReady Compliance

- UEFI Secure Boot

- Virtualization <sup>[1]</sup>

- IO virtualization

- Virtual Interrupts And VGIC

- KVM Unit Test

- Booting Distro as a VM

- Non-discoverable IO Virtualization block

- Trusted Firmware-A Tests <sup>[1]</sup>

- Virtio-P9

- Low power idle

- Collaborative processor performance control

Follow the links above for detailed information about the build and execute steps for each of the supported features.

[1] Build and boot not supported on AArch64 host machines.

# 13.3 Obtaining FVP

The latest version of the RD-V2 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse V2 Reference Design FVP" link to obtain the list of available Neoverse RD-V2 Reference Design FVPs.

- Select a FVP build based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-V2 FVP executable is included in the downloaded installer and named as "FVP\_RD\_V2". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 13.4 Release Tags

Table below lists the release tags for the RD-V2 platform software stack and the corresponding RD-V2 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-V2 FVP Version |

|---------------------|-------------------|

| RD-INFRA-2024.12.20 | 11.24.12          |

| RD-INFRA-2024.09.30 | 11.24.12          |

| RD-INFRA-2024.07.15 | 11.24.12          |

| RD-INFRA-2024.04.17 | 11.24.12          |

| RD-INFRA-2023.12.22 | 11.24.12          |

| RD-INFRA-2023.09.29 | 11.20.18          |

| RD-INFRA-2023.06.30 | 11.20.18          |

| RD-INFRA-2023.03.31 | 11.20.18          |

#### FOURTEEN

# **RD-N2 CFG3 PLATFORM**

#### 14.1 Overview

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-N2 Cfg3 platform (which is a variant of the the *RD-N2* platform) in particular is based on the following hardware configuration.

- 16xMP1 Neoverse N2 CPUs

- CMN-700 interconnect (mesh size 10x6)

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

The components integrated into this stack are described in Software Stack section.

# **14.2 Supported Features**

RD-N2 Cfg3 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Linux Distribution Boot

- Arm SystemReady Compliance

- UEFI Secure Boot

- Virtualization <sup>[1]</sup>

- IO virtualization

- Virtual Interrupts And VGIC

- KVM Unit Test

- Booting Distro as a VM

- Non-discoverable IO Virtualization block

- Virtio-P9

Follow the links above for detailed information about the build and execute steps for each of the supported features.

[1] Build and boot supported on AArch64 host machines as well.

# 14.3 Obtaining FVP

The latest version of the RD-N2 Cfg3 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse N2 Reference Design FVP" link to obtain the list of available Neoverse RD-N2 Reference Design FVPs.

- Select a FVP build under the section "Download RD-N2 Cfg3" based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-N2 Cfg3 FVP executable is included in the downloaded installer and named as "FVP\_RD\_N2\_Cfg3". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 14.4 Release Tags

Table below lists the release tags for the RD-N2 Cfg3 platform software stack and the corresponding RD-N2 Cfg3 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-N2 Cfg3 FVP Version |

|---------------------|------------------------|

| RD-INFRA-2024.12.20 | 11.25.23               |

| RD-INFRA-2024.09.30 | 11.25.23               |

| RD-INFRA-2024.07.15 | 11.25.23               |

| RD-INFRA-2024.04.17 | 11.25.23               |

| RD-INFRA-2023.12.22 | 11.24.12               |

| RD-INFRA-2023.09.29 | 11.20.18               |

| RD-INFRA-2023.06.30 | 11.20.18               |

| RD-INFRA-2023.03.31 | 11.20.18               |

#### **FIFTEEN**

# **RD-N2 CFG2 PLATFORM**

### **15.1 Overview**

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-N2 Cfg2 platform (which is a variant of the the *RD-N2* platform) is a quad-chip platform in which four identical chips are connected through high speed CCG link. The CCG link is enabled through CMN-700 Coherent Multichip Link (CML) feature. RD-N2 Cfg2 in particular has the following hardware configuration on each chip.

- 4xMP1 Neoverse N2 CPUs

- CMN-700 interconnect (mesh size 6x6)

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

The components integrated into this stack are described in Software Stack section.

# **15.2 Supported Features**

RD-N2 Cfg2 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Linux Distribution Boot

- Low power idle

- Collaborative processor performance control

Follow the links above for detailed information about the build and execute steps for each of the supported features.

# 15.3 Obtaining FVP

The latest version of the RD-N2 Cfg2 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse N2 Reference Design FVP" link to obtain the list of available Neoverse RD-N2 Reference Design FVPs.

- Select a FVP build under the section "Download RD-N2" based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-N2 Cfg2 FVP executable is included in the downloaded installer and named as "FVP\_RD\_N2\_Cfg2". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 15.4 Release Tags

Table below lists the release tags for the RD-N2 Cfg2 platform software stack and the corresponding RD-N2 Cfg2 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-N2 Cfg2 FVP Version |

|---------------------|------------------------|

| RD-INFRA-2024.12.20 | 11.25.23               |

| RD-INFRA-2024.09.30 | 11.25.23               |

| RD-INFRA-2024.07.15 | 11.25.23               |

| RD-INFRA-2024.04.17 | 11.25.23               |

| RD-INFRA-2023.12.22 | 11.24.12               |

| RD-INFRA-2023.09.29 | 11.20.18               |

| RD-INFRA-2023.06.30 | 11.20.18               |

| RD-INFRA-2023.03.31 | 11.20.18               |

#### SIXTEEN

## **RD-N2 CFG1 PLATFORM**

#### 16.1 Overview

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-N2 Cfg1 platform (which is a variant of the the *RD-N2* platform) in particular is based on the following hardware configuration.

- 8xMP1 Neoverse N2 CPUs

- CMN-700 interconnect (mesh size 3x3)

- · Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

The components integrated into this stack are described in Software Stack section.

## **16.2 Supported Features**

RD-N2 Cfg1 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Linux Distribution Boot

- UEFI Secure Boot

- Non-discoverable IO Virtualization block

- Virtualization <sup>[1]</sup>

- IO virtualization

- Virtual Interrupts And VGIC

- KVM Unit Test

- Booting Distro as a VM

- Reliability, Availability, and Serviceability

- RD-N2 CPU/RAM Error Injection Tests

- Trusted Firmware-A Tests <sup>[1]</sup>

- Virtio-P9

- MPAM-resctrl

- Low power idle

- Collaborative processor performance control

Follow the links above for detailed information about the build and execute steps for each of the supported features.

[1] Build and boot not supported on AArch64 host machines.

# 16.3 Obtaining FVP

The latest version of the RD-N2 Cfg1 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse N2 Reference Design FVP" link to obtain the list of available Neoverse RD-N2 Reference Design FVPs.

- Select a FVP build under the section "Download RD-N2 Cfg1" based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-N2 Cfg1 FVP executable is included in the downloaded installer and named as "FVP\_RD\_N2\_Cfg1". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 16.4 Release Tags

Table below lists the release tags for the RD-N2 Cfg1 platform software stack and the corresponding RD-N2 Cfg1 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-N2 Cfg1 FVP Version |

|---------------------|------------------------|

| RD-INFRA-2024.12.20 | 11.25.23               |

| RD-INFRA-2024.09.30 | 11.25.23               |

| RD-INFRA-2024.07.15 | 11.25.23               |

| RD-INFRA-2024.04.17 | 11.25.23               |

| RD-INFRA-2023.12.22 | 11.24.12               |

| RD-INFRA-2023.09.29 | 11.20.18               |

| RD-INFRA-2023.06.30 | 11.20.18               |

| RD-INFRA-2023.03.31 | 11.20.18               |

### SEVENTEEN

# **RD-N2 PLATFORM**

## **17.1 Overview**

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-N2 in particular is based on the following hardware configuration.

- 32xMP1 Neoverse N2 CPUs

- CMN-700 interconnect

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

The Fixed Virtual Platform of RD-N2 config supports 16xMP1 Neoverse N2 CPUs.

The components integrated into this stack are described in Software Stack section.

# **17.2 Supported Features**

RD-N2 platform software stack supports the following features.

- Busybox Boot

- Buildroot boot

- Linux Distribution Boot

- Arm SystemReady Compliance

- UEFI Secure Boot

- Virtualization <sup>[1]</sup>

- IO virtualization

- Virtual Interrupts And VGIC

- KVM Unit Test

- Booting Distro as a VM

- Non-discoverable IO Virtualization block

- Trusted Firmware-A Tests <sup>[1]</sup>

- Virtio-P9

- Low power idle

- Collaborative processor performance control

Follow the links above for detailed information about the build and execute steps for each of the supported features.

[1] Build and boot not supported on AArch64 host machines.

# 17.3 Obtaining FVP

The latest version of the RD-N2 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page,

- Navigate to "Neoverse Infrastructure FVPs" section.

- Click on "Neoverse N2 Reference Design FVP" link to obtain the list of available Neoverse RD-N2 Reference Design FVPs.

- Select a FVP build under the section "Download RD-N2" based on the host machine architecture.

- For AArch64 host machine, click "Download Linux Arm Host (DEV)" link.

- For x86-64 host machine, click "Download Linux" link.

The RD-N2 FVP executable is included in the downloaded installer and named as "FVP\_RD\_N2". Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 17.4 Release Tags

Table below lists the release tags for the RD-N2 platform software stack and the corresponding RD-N2 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-N2 FVP Version |

|---------------------|-------------------|

| RD-INFRA-2024.12.20 | 11.25.23          |

| RD-INFRA-2024.09.30 | 11.25.23          |

| RD-INFRA-2024.07.15 | 11.25.23          |

| RD-INFRA-2024.04.17 | 11.25.23          |

| RD-INFRA-2023.12.22 | 11.24.12          |

| RD-INFRA-2023.09.29 | 11.20.18          |

| RD-INFRA-2023.06.30 | 11.20.18          |

| RD-INFRA-2023.03.31 | 11.20.18          |

#### EIGHTEEN

### **RD-V1 MC PLATFORM**

#### **18.1 Overview**

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP.

RD-V1 MC is a quad-chip platform in which four identical chips are connected through high speed CCIX link. The CCIX link is enabled through CMN-650 Coherent Multichip Link (CML) feature. RD-V1 MC in particular is based on the following hardware configuration.

- 128xMP1 Neoverse V1 CPUs

- CMN-650 interconnect

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

The Fixed Virtual Platform of RD-V1 MC supports a reduced configuration of the above configuration. That is, there are a total of 16xMP1 Neoverse V1 CPUs, 4xMP1 Neoverse CPUs on each chip on RD-V1 MC FVP.

The components integrated into this stack are described in Software Stack section.

# **18.2 Supported Features**

RD-V1 MC platform software stack supports the following features.

- Busybox Boot.

- Low power idle

- Collaborative processor performance control

Follow the links above for detailed information about the build and execute steps for each of the supported features.

# 18.3 Obtaining FVP

The latest version of the RD-V1 MC fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page, navigate to "Neoverse Infrastructure FVPs" section to download the RD-V1 platform FVP installer.

Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 18.4 Release Tags

Table below lists the release tags for the RD-V1 Quad-Chip platform software stack and the corresponding RD-V1 MC FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-V1 MC FVP Version |

|---------------------|----------------------|

| RD-INFRA-2024.12.20 | 11.17.29             |

| RD-INFRA-2024.09.30 | 11.17.29             |

| RD-INFRA-2024.07.15 | 11.17.29             |

| RD-INFRA-2024.04.17 | 11.17.29             |

| RD-INFRA-2023.12.22 | 11.17.29             |

| RD-INFRA-2023.09.29 | 11.17.29             |

| RD-INFRA-2023.06.30 | 11.17.29             |

| RD-INFRA-2023.03.31 | 11.17.29             |

#### NINETEEN

## **RD-V1 PLATFORM**

#### **19.1 Overview**

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-V1 in particular is based on the following hardware configuration.

- 32xMP1 Neoverse V1 CPUs

- CMN-650 interconnect

- · Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

The Fixed Virtual Platform of RD-V1 supports 16xMP1 Neoverse V1 CPUs.

The components integrated into this stack are described in Software Stack section.

# **19.2 Supported Features**

RD-V1 platform software stack supports the following features.

- Busybox Boot

- Linux Distribution Boot

- Low power idle

- Collaborative processor performance control

Follow the links above for detailed information about the build and execute steps for each of the supported features.

# 19.3 Obtaining FVP

The latest version of the RD-V1 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page, navigate to "Neoverse Infrastructure FVPs" section to download the RD-V1 platform FVP installer.

Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 19.4 Release Tags

Table below lists the release tags for the RD-V1 platform software stack and the corresponding RD-V1 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-V1 FVP Version |

|---------------------|-------------------|

| RD-INFRA-2024.12.20 | 11.17.29          |

| RD-INFRA-2024.09.30 | 11.17.29          |

| RD-INFRA-2024.07.15 | 11.17.29          |

| RD-INFRA-2024.04.17 | 11.17.29          |

| RD-INFRA-2023.12.22 | 11.17.29          |

| RD-INFRA-2023.09.29 | 11.17.29          |

| RD-INFRA-2023.06.30 | 11.17.29          |

| RD-INFRA-2023.03.31 | 11.17.29          |

#### TWENTY

## **RD-N1 EDGE X2 PLATFORM**

#### 20.1 Overview

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-N1 Edge in particular is based on the following hardware configuration.

- 8x Neoverse N1 Cores with DynamIQ Shared Unit (DSU)

- Dedicated L2 cache: 512KB per core

- Shared L3 cache: 2MB per cluster

- CMN-600 with CML option: 8MB System Level Cache and 16MB Snoop Filter

- DMC-620 with 2xRDIMM DDR4-3200

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

RD-N1 Edge dual-chip is a platform configuration in which two RD-N1 Edge platforms are connected through high speed CCIX link. The CCIX link is enabled by CMN600's Coherent Multichip Link. Such platforms are called RD-N1 Edge-Dual hereafter.

The components integrated into this stack are described in *Software Stack* section.

# **20.2 Supported Features**

RD-N1 Edge-Dual platform software stack supports the following features.

- Busybox Boot.

- Low power idle

Follow the links above for detailed information about the build and execute steps for each of the supported features.

# 20.3 Obtaining FVP

The latest version of the RD-N1 Edge-Dual fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page, navigate to "Neoverse Infrastructure FVPs" section to download the RD-N1 Edge platform FVP installer.

Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 20.4 Release Tags

Table below lists the release tags for the RD-N1 Edge dual-chip platform software stack and the corresponding RD-N1 Edge dual-chip FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-N1 Edge-Dual FVP Version |

|---------------------|-----------------------------|

| RD-INFRA-2024.12.20 | 11.17.29                    |

| RD-INFRA-2024.09.30 | 11.17.29                    |

| RD-INFRA-2024.07.15 | 11.17.29                    |

| RD-INFRA-2024.04.17 | 11.17.29                    |

| RD-INFRA-2023.12.22 | 11.17.29                    |

| RD-INFRA-2023.09.29 | 11.17.29                    |

| RD-INFRA-2023.06.30 | 11.17.29                    |

| RD-INFRA-2023.03.31 | 11.17.29                    |

#### TWENTYONE

## **RD-N1 EDGE PLATFORM**

### 21.1 Overview

RD (Reference Design) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. RD-N1 Edge in particular is based on the following hardware configuration.

- 8x Neoverse N1 Cores with DynamIQ Shared Unit (DSU)

- Dedicated L2 cache: 512KB per core

- Shared L3 cache: 2MB per cluster

- CMN-600 with CML option: 8MB System Level Cache and 16MB Snoop Filter

- DMC-620 with 2xRDIMM DDR4-3200

- Multiple AXI expansion ports for I/O Coherent PCIe, Ethernet, offload

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

The components integrated into this stack are described in Software Stack section.

# **21.2 Supported Features**

RD-N1 Edge platform software stack supports the following features.

- Busybox Boot.

- Linux Distribution Boot

- Low power idle

Follow the links above for detailed information about the build and execute steps for each of the supported features.

# 21.3 Obtaining FVP

The latest version of the RD-N1 Edge fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page, navigate to "Neoverse Infrastructure FVPs" section to download the RD-N1 Edge platform FVP installer.

Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 21.4 Release Tags

Table below lists the release tags for the RD-N1 Edge platform software stack and the corresponding RD-N1 Edge FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | RD-N1 Edge FVP Version |

|---------------------|------------------------|

| RD-INFRA-2024.12.20 | 11.17.29               |

| RD-INFRA-2024.09.30 | 11.17.29               |

| RD-INFRA-2024.07.15 | 11.17.29               |

| RD-INFRA-2024.04.17 | 11.17.29               |

| RD-INFRA-2023.12.22 | 11.17.29               |

| RD-INFRA-2023.09.29 | 11.17.29               |

| RD-INFRA-2023.06.30 | 11.17.29               |

| RD-INFRA-2023.03.31 | 11.17.29               |

# CHAPTER TWENTYTWO

# SGI-575 PLATFORM

## 22.1 Overview

SGI (System Guidance for Infrastructure) is a collection of resources to provide a representative view of typical compute subsystems that can be designed and implemented using specific generations of Arm IP. SGI-575 in particular is based on the following hardware configuration.

- 8x Cortex-A75 with private L2 Cache

- DynamIQ with L3 Cache options

- System Level Cache options

- Up to 2x DDR4-3200 (DMC-620)

- Arm Cortex-M7 for System Control Processor (SCP) and Manageability Control Processor (MCP)

The components integrated into this stack are described in Software Stack section.

# 22.2 Supported Features

SGI-575 platform software stack supports the following features.

- Busybox Boot

- Low power idle

Follow the links above for detailed information about the build and execute steps for each of the supported features.

# 22.3 Obtaining the FVP

The latest version of the SGI-575 fixed virtual platform (FVP) can be downloaded from the Arm Ecosystem FVPs page. On this page, navigate to "Neoverse Infrastructure FVPs" section to download the SGI-575 platform FVP installer.

Follow the instructions of the installer and setup the FVP. The installer, by default, selects the home directory to install the FVP. To opt for different directory than the one selected by the installer, provide an absolute path to that directory when prompted for during the FVP installation process.

# 22.4 Release Tags

Table below lists the release tags for the SGI-575 platform software stack and the corresponding SGI-575 FVP version that is recommended to be used along with the listed release tag. The summary of the changes introduced and tests validated in each release is listed in the release note, the link to which is in the 'Release Tag' column in the table below.

| Release Tag         | SGI-575 FVP Version |

|---------------------|---------------------|

| RD-INFRA-2024.09.30 | 11.15.26            |

| RD-INFRA-2024.07.15 | 11.15.26            |

| RD-INFRA-2024.04.17 | 11.15.26            |

| RD-INFRA-2023.12.22 | 11.15.26            |

| RD-INFRA-2023.09.29 | 11.15.26            |

| RD-INFRA-2023.06.30 | 11.15.26            |

| RD-INFRA-2023.03.31 | 11.15.26            |

### TWENTYTHREE

# AP BOOT FROM BL31 (RESET TO BL31 FLOW)

**Important:** This feature might not be applicable to all platforms. Please check individual platform pages, section **Supported Features** to confirm if this feature is listed as supported.

## 23.1 Overview of Reset to BL31

Trusted Firmware-A (TF-A) has three bootloader stages called BL1, BL2 and BL31. BL1 and BL2 serve the purpose of platform initialization and loading other firmware images (including BL31). BL31 is the runtime resident. TF-A has a feature called RESET\_TO\_BL31 which allows the application processor to reset directly to the BL31 stage, bypassing BL1 and BL2.

# 23.2 Building the platform software

**Note:** This section assumes the user has completed the chapter *Getting Started* and has a functional working environment.

Reset to BL31 is disabled for all platforms by default. To build the platform software for Reset to BL31 boot flow, an environment variable \$PLAT\_RESET\_AP\_TO\_BL31 needs to be set to 1. If this variable is not defined or is set to 0, Reset to BL31 remains disabled. Any values other than 0 and 1 will result in a build failure.

When \$PLAT\_RESET\_AP\_TO\_BL31 is 1, all the AP binaries that are needed for the setup of subsequent images are preloaded in the model.

For example, to build the software for Busybox boot, the commands are as follows:

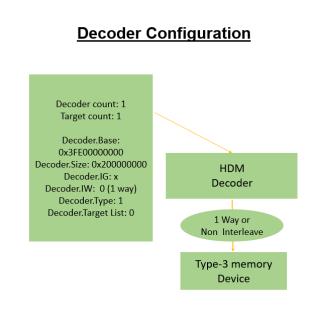

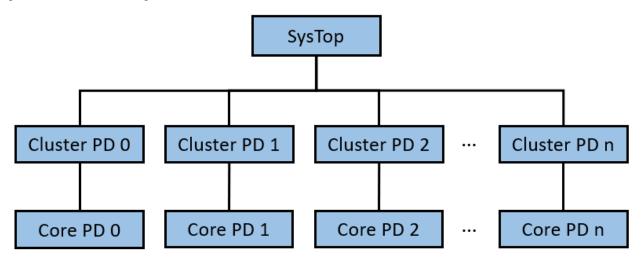

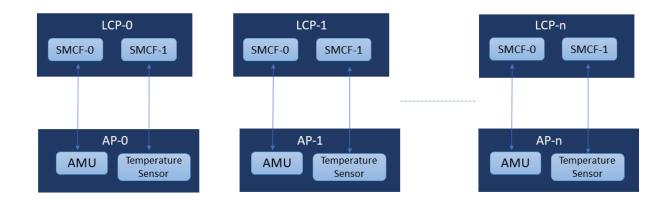

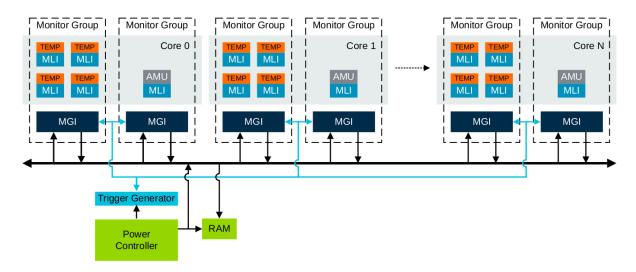

```